2521/203, 2602/202 2601/202, 2603/202 DIGITAL AND ANALOGUE ELECTRONICS II June/July 2020 Time: 3 hours

## THE KENYA NATIONAL EXAMINATIONS COUNCIL

# DIPLOMA IN ELECTRICAL AND ELECTRONIC ENGINEERING (POWER OPTION) (TELECOMMUNICATION OPTION) (INSTRUMENTATION OPTION) MODULE II

DIGITAL AND ANALOGUE ELECTRONICS II

3 hours

### INSTRUCTIONS TO CANDIDATES

You should have the following for this examination.

Answer booklet:

Mathematical table/Non-programmable scientific calculator;

Drawing instruments.

The paper consists of EIGHT questions in TWO sections, A and B.

Answer any TWO questions from section A and any THREE questions from section B in the answer booklet provided.

All questions carry equal marks.

Maximum marks for each part of a question are as indicated.

Candidates should answer the questions in English,

This paper consists of 8 printed pages.

Candidates should check the question paper to ascertain that all the pages are printed as indicated and that no questions are missing.

# SECTION A: ANALOGUE ELECTRONICS II

Answer any TWO questions from this section.

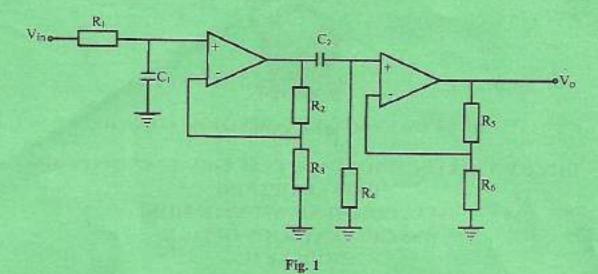

(a) Figure 1 shows a circuit diagram of an active filter.

- (i) identify the type of the filter;

- (ii) draw its labelled frequency response curve;

- (iii) describe its operation.

(7 marks)

(b) A transistor in a common-base amplifier circuit has the following h-parameter values:  $h_{ab} = 28\Omega$ ;  $h_{ab} = -0.98$ ;  $h_{ab} = 5 \times 10^{-4}$ ;  $h_{ab} = -0.34 \times 10^{-6}$  S and load resistance  $r_1 = 1.21 \text{k} \Omega$ .

Determine the:

- (i) current gain;

- (ii) input resistance;

- (iii) voltage gain.

(9 marks)

(c) State four applications of a triac.

(4 marks)

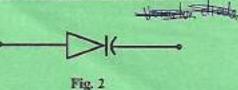

(a) Figure 2 shows a symbol of a semiconductor device.

- (i) identify the device;

- (ii) explain the operation of the device.

(5 marks)

- (b) The intrinsic stand-off ratio of a unijunction transistor (UJT) is 0.65 and the interbase resistance is 7.5 kΩ, determine the:

- r<sub>B1</sub>;

- (ii) rn2.

(5 marks)

- (c) (i) Define each of the following with reference to thyristors:

- (I) break over voltage; and the stand

- (II) peak reverse voltage a note many vertice ARI ( ) the hope of hope of the state of the state

- (ii) With the aid of a V-I characteristic curve describe the operation of a silicon controlled rectifier (SCR). The state of the controlled rectifier (SCR). The state of the controlled rectifier (SCR) and the controlled rectifier (SCR).

- 3. (a) State two characteristics of a laser light. 15 to any a food able within a giren (2 marks)

- (b) List two conditions necessary for sustained oscillations in oscillators. (2 marks)

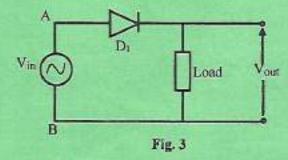

- Figure 3 shows an electric circuit. With the aid of waveforms explain its operation.

(6 marks)

- (d) (i) With the aid of a circuit diagram describe the operation of a blocking oscillator.

- (ii) State two applications of oscillators.

(10 marks)

### SECTION B: DIGITAL ELECTRONICS

Answer any THREE questions from this section.

- 1

- (a) Perform each of the following number system conversions:

- (i) 7562.45<sub>10</sub> to octal;

- (ii) 1938.85<sub>10</sub> to hexadecimal;

- (iii) 11010.1112 to decimal.

(11 marks)

- (b) (i) Using Boolean algebra simplify the following expressions:

- (I) ABC + AB + ABC:

- (II)  $AB + (\overline{A} + \overline{B})C + A$ .

- (ii) Convert the binary number 11101 to Gray code.

(9 marks)

- (a) (i) Define each of the following as applied to analogue to digital converters (ADCs).

- accuracy;

- (II) resolution;

- (III) conversion time.

- (ii) A 10-bit ramp type analogue to digital converter is driven by a 1 MHz clock. Determine the:

- maximum conversion time;

- (II) average conversion time;

- (III) .maximum rate of conversion.

(8 marks)

(b) An 8-bit digital system uses the following memory address ranges:

0000H - 07FF H: ROM 2000H - 23FF H: RAM

If the available chips are 1 k × 8 ROM and 0.5 k × 4 RAM, determine the:

- (i) size of ROM and RAM in kilobytes;

- (ii) number of chips required for each memory type.

(12 marks)

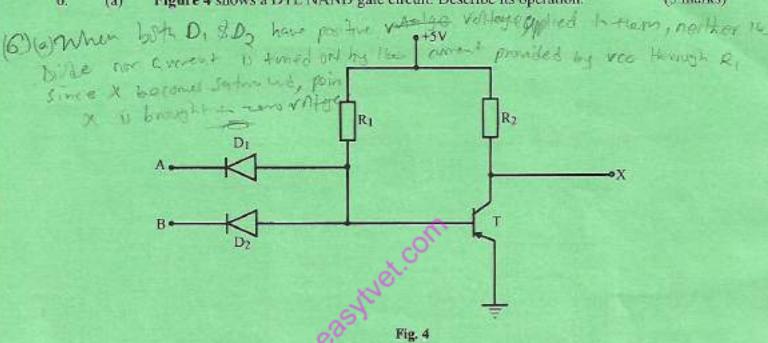

6. (a) Figure 4 shows a DTL NAND gate circuit. Describe its operation.

(5 marks)

- (b) (i) Define each of the following as applied in sequential circuits:

- (1) set-up time; In the time before trigger

- (II) maximum clocking frequency;

- (III) hold time. It the time of the trager

- (ii) A four stage binary ripple counter has a propagation delay of 40 ns in each flip flop. Determine the:

- (I) total propagation delay; 1) 111 = 400 1 = 1600 s

- (II) maximum operating frequency,

(7 marks)

2521/203 2602/202 2601/202 2603/202 June/July 2020 May =

5

Turn over

- (c) A security firm intends to install an alarm system with 3 motion sensors A, B and C. To prevent false alarms produced by a single sensor activation, the alarm will be triggered only when at least two sensors are activated simultaneously.

- (i) Draw the truth table for the alarm system;

- Obtain a simplified Boolean expression of the system using a Karnaugh map.

(8 marks)

- (a) (i) Distinguish between synchronous and asynchronous counters.

- State three applications of binary counters.

(5 marks)

- (b) (i) Draw a schematic diagram of a 4-bit ring counter using D-type flip flops.

- (ii) Draw the counting sequence waveforms for the counter in b (i).

(7 marks)

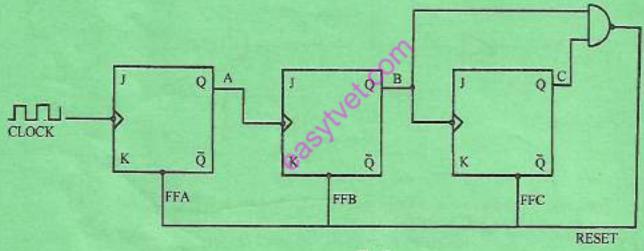

(c) Figure 5 shows a logic diagram of a binary counter.

- Fig. 5

- (i) Explain its operation;

- (ii) Draw the state transition diagram for the counter.

(8 marks)

2521/203 2602/202 2601/202 2603/202 June/July 2020

- 8. (a) (i) State De-Morgans theorems.

- (ii) Using De-Morgans theorems simplify the expression:

$$F = (\overline{X \ \overline{Y}})(\overline{Y} + Z)$$

(5 marks)

- (b) (i) Draw the truth table of a half subtractor circuit.

- (ii) Obtain the Boolean expression for the circuit in b, (i)

- (iii) Using logic gates implement the expression obtained in b (ii) (9 marks)

- (c) With the aid of a diagram, describe the operation of a CMOS inverter. (6 marks)

(ii) The reversed brassed voltage

increases the clepletion layer

widens it increases the

die lectric thickness which

Interns reduce the capacitance

when the reveres brased voltage

is cleavensed.

The depletion layer narrows

down this decreases the electric

thickness which interns increases

the capacitance.

2521/203 2602/202

$$0.65 \times 7.5$$

7

2601/202 2603/202  $0.65 \times 7.5$   $= 4.875 \text{ k.s.}$

Turn over